Parallel Input Serial Output Shift Register Verilog Code

VHDL and Verilog Codes. Saturday, 13 July 2013. Output out; input s,l,i,q; wire andod,andevn; and od (andod,q,s) Left shift register. Parallel in parallel out (pipo).

Link for the coupons : Here

--------------------------------------------------------------------------------------------------------------------

Adders in Vlsi are basic components for an ALU . There are N number of adders each with their own advantages & disadvantages. When two numbers are to be added and if each of them is of N bits than we can add them in Two different ways :

- Serial

- Parallel

In serial addition the LSB's are added first than the carry created are propagated to the next higher bits. Whereas in parallel addition every it added in parallel without waiting for carry and different algorithms are used to compensate for the carry.

Carry bits are to handled properly so that the resulting answer after addition is correct.But as we know that for each addition there can be a carry generated can it has to be accounted for. When we try doing this the major criteria to be kept in mind are propagation time and time taken to calculate the carry. Here are few Verilog codes for different types of adders:

>>>Verilog code for Half adder

>>>Verilog code for Full adder

>>>Verilog code for Parallel adder

>>>Verilog code for CLA(carry look ahead affer)

>>>Verilog code for RCA(Ripple carry adder)

>>>Verilog code for 32 Bit Pipelined Floating Point Adder

>>>Verilog code for Carry Save Adder

>>>Verilog Code for Carry Select Adder

halfadder(a,b,sum,carry);

output sum, carry;

assign sum = a^b; // sum bit

//carry bit

Verilog code for Full adder

module fulladder(a,b,c,sum,carry);

output sum,carry;

assign sum=a^b^c; // sum bit

endmodule

output [3:0]a;

input [3:0]p,q;

hau1(a[0],c1,p[0],q[0]);

fau3(a[2],c3,p[2],q[2],c2);

endmodule

module cla32( d1,d2,clk,cin,sum,cout); //32 bit CLA using 84-bit CLA adderes

input [31:0] d2;

input cin;

output [31:0] sum;

reg [31:0] b;

begin

b<=-d2-1;

b<=d2;

cla4 n1(d1[3:0],b[3:0],cin,sum[3:0],c0);

cla4 n3(d1[11:8],b[11:8],c1,sum[11:8],c2);

cla4 n5(d1[19:16],b[19:16],c3,sum[19:16],c4);

cla4 n7(d1[27:24],b[27:24],c5,sum[27:24],c6);

endmodule

module cla4(a,b,cin,s,cout);

input cin;

output[3:0] s;

wire[13:0] z;

and21 x2 (.a1(a[0]),.a2(b[0]),.z(g[0]));

and21 x4 (.a1(a[1]),.a2(b[1]),.z(g[1]));

and21 x6 (.a1(a[2]),.a2(b[2]),.z(g[2]));

and21 x8 (.a1(a[3]),.a2(b[3]),.z(g[3]));

and21 x10 (.a1(cin),.a2(p[0]),.z(z[0]));

xor21 x12 (.a1(z[1]),.a2(p[1]),.z(s[1]));

and31 x13 (.a1(cin),.a2(p[0]),.a3(p[1]),.z(z[2]));

or31 x15 (.a1(z[2]),.a2(z[3]),.a3(g[1]),.z(z[4]));

and41 x17 (.a1(cin),.a2(p[0]),.a3(p[1]),.a4(p[2]),.z(z[5]));

and31 x18 (.a1(g[0]),.a2(p[1]),.a3(p[2]),.z(z[6]));

or41 x20 (.a1(z[5]),.a2(z[6]),.a3(z[7]),.a4(g[2]),.z(z[8]));

and41 x22 (.a1(cin),.a2(p[0]),.a3(p[1]),.a4(p[2]),.z(z[9]));

and31 x23 (.a1(g[0]),.a2(p[1]),.a3(p[2]),.z(z[10]));

or41 x25 (.a1(z[9]),.a2(z[10]),.a3(z[11]),.a4(g[2]),.z(z[12]));

or21 x27 (.a1(z[13]),.a2(g[3]),.z(cout));

//main module of 16 bit Ripple carry adder

input [15:0]b;

output cout;

wire c4,c8,c12,cout;

rip2 m2(s[7:4],c8,a[7:4],b[7:4],c4);

rip2 m4(s[15:12],cout,a[15:12],b[15:12],c12);

//sub module for 4 bit Ripple carry adder

input [3:0]b;

output cout;

wire c2,c3,c4,cout;

fa m2(s[1],c3,a[1],b[1],c2);

fa m4(s[3],cout,a[3],b[3],c4);

//sub module for Full adder

output s,cout;

ha m1(w1,w2,a,b);

or m3(cout,w2,w3);

//sub module for Half adder

output s,cout;

and m2(cout,a,b);

Verilog code for 32 Bit PipelinedFloating Point Adder :

module fpadd(a,b,clk,out);

input clk;

wire [7:0]e1,e2,ex,ey,exy,ex1,ey1,ex2,ex3;

wire s1,s2,s,s3,sr,sn,s4,sx1,sy1,sn1,sn2,sn3,sn4,sr1,sr2,sn5,sn6;

wire [24:0]mxy1,mxy2;

assign s2=b[31];

assign e2=b[30:23];

assign m2[23]=1'b1;

assign m2[22:0]=b[22:0];

cmpshiftas(e1[7:0],e2[7:0],s1,s2,m1[23:0],m2[23:0],clk,ex,ey,mx,my,s,sx1,sy1);

buffer1 buff1(ex,ey,sx1,sy1,mx,my,s,clk,ex1,ey1,mx1,my1,sn,sn1,sn2);

//sub module for mantissa addition snd subtraction

faddsub as1(mx1,my1,sn1,sn2,sn,ex1,clk,mxy1,ex2,sn3,sn4,s3,sr1);

buffer2 buff2(mxy1,s3,sr1,ex2,sn3,sn4,clk,mxy2,ex3,sn5,sn6,s4,sr2);

normalized as2(mxy2,sr2,sn5,sn6,s4,clk,ex3,sr,exy,mxy);

endmodule

module buffer2(mxy1,s3,sr1,ex,sn3,sn4,clk,mxy2,ex3,sn5,sn6,s4,sr2);

input s3,clk,sr1,sn3,sn4;

output reg[24:0]mxy2;

output reg s4,sn5,sn6,sr2;

begin

sn5=sn3;

ex3=ex;

s4=s3;

endmodule

module buffer1(ex,ey,sx1,sy1,mx,my,s,clk,ex1,ey1,mx1,my1,sn,sn1,sn2);

input [23:0]mx,my;

output reg [7:0]ex1,ey1;

output reg sn,sn1,sn2;

begin

sn2=sy1;

ey1=ey;

my1=my;

end

module normalized(mxy1,s,s1,s2,s3,clk,ex,sr,exy,mxy);

input s,s1,s2,s3,clk;

output reg sr;

output reg[23:0]mxy;

always@(posedge clk)

sr=s?s1^(mxy1[24]&s3):s2^(mxy1[24]&s3);

mxy=mxy2[24:1];

repeat(24)

if(mxy[23]1'b0)

mxy=mxy<<1 b1=' o:p='>

end

end

module faddsub(a,b,s1,s2,sn,ex1,clk,out,ex2,sn3,sn4,s,sr1); //submodulefor addition or subtraction

input[7:0]ex1;

output reg [23:0]ex2;

output reg s,sn3,sn4,sr1;

begin

sr1=sn;

sn4=s2;

if(s)

out=a-b;

else

out=a+b;

end

module cmpshift(e1,e2,s1,s2,m1,m2,clk,ex,ey,mx,my,s,sx1,sy1); //module forcopare &shift

input [23:0]m1,m2;

output reg[7:0]ex,ey;

output reg s,sx1,sy1;

always@(posedge clk)

sx1=s1;

if(e1e2)

ex=e1+8'b1;

mx=m1;

s=1'b1;

else if(e1>e2)

diff=e1-e2;

ey=e1+8'b1;

my=m2>>diff;

end

begin

ex=e2+8'b1;

mx=m2;

s=1'b0;

end

Verilog code for BCD Adder:

module bcdadd(a,b,cin,s,cout); //Main module of one digitBCD adder

input [3:0]b;

output[3:0]s;

wire [3:0]w;

fulladd m1(a[0],b[0],cin,w[0],c0);

fulladd m3(a[2],b[2],c1,w[2],c2);

assign y=c3 (w[3]&(w[2] w[1]));

fulladd m6(w[2],y,c4,s[2],c5);

assign s[0]=w[0];

module fulladd(a,b,cin,s,cout); //submodule for fulladder

input cin;

output cout;

halfadd g1(a,b,w1,w2);

assign cout=w3 w2;

module halfadd(a,b,s,cout); //submodule for halfadder

output s,cout;

assign cout=a&b;

Verilog code for Carry Save Adder:

modulecarrysave(p0,p1,p2,p3,p4,p5,s,c,a,b);

output [10:0]s;

input [5:0]a,b;

wire d,d1,d2,d3,d4,d5,d6,d7,d8,d9,d10,d11,d12,d13,d14,d15,d16,d17,e1,e2,e3,e4,e5,e6,e7,e8,e9,e10,e11,e13,e14,e15,e16,e17;

assign p0=b[0]?a:0;

assign p2=b[2]?a:0;

assign p4=b[4]?a:0;

assign s[0]=p0[0];

HA h1(s[1],d,p0[1],p1[0]);

FA m1(e1,d1,p0[2],p1[1],p2[0]);

FA m3(e3,d3,p0[4],p1[3],p2[2]);

HA h4(e11,d11,p4[5],p5[4]);

FA m6(e8,d8,p3[3],p4[2],p5[1]);

FA m8(e10,d10,p3[5],p4[4],p5[3]);

HA h5(s[2],d12,d,e1);

FA m10(e14,d14,d2,e3,e6);

FA m12(e16,d16,d4,e5,e8);

HA h6(s[3],c[0],d12,e13);

Serial Input Serial Output Shift Register

HA h8(s[9],c[6],d10,e11);

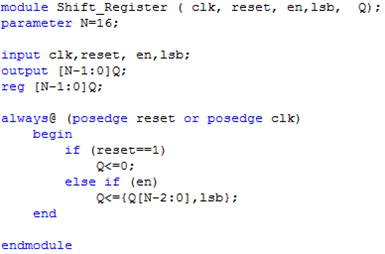

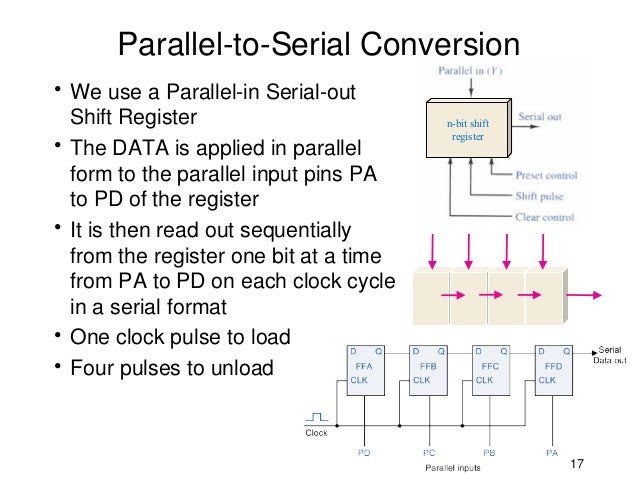

Parallel Input Serial Output Shift Registers

FA m14(s[5],c[2],d6,d14,e15);

FA m16(s[7],c[4],d8,d16,e17);

endmodule

Verilog Code for Carry Select Adder:

module uniformcarryadder(s0,s1,s2,i0,i1,i2,i3,i4,i5);

output [3:0] s0,s1,s2;

wire w6,w7;

adder fa2(s2,s3,c0,c2,i2,i3);

mux m2(cc1,ss1,s2,c2,w2,w3,w6);

endmodule

module adder(vs1,vvs1,vc0,vvc0,a,b);

output [3:0] vc0,vs1;

assign {vc0,vvs0}=a+b;

endmodule

module mux(cp,sum,s0,s1,c0,c1,cin);

input c0,c1,cin;

assign {cp,sum}= cin? {c0,s0}:{c1,s1};